接地:您需要了解ESD和RF设备的信息(第1部分)

July 26, 2018

This is the first blog in a three-part series looking at ESD protection in mobile handsets.

This is the first blog in a three-part series looking at ESD protection in mobile handsets.

这electrostatic discharge(ESD)自从时间开始以来一直存在现象。当您在干燥的寒冷的日子触摸金属门把手时,我们最常用的eSD的第一次经历往往是童年。ZAP,你会震惊 - 礼貌静电放电。这种瞬间不适通常对人类不成问题,但甚至可以通过少量ESD来破坏敏感的电路。

移动设计人员继续面临何时以及如何解决这种自然现象的挑战。此博客解释了为什么系统级ESD保护事项,提供有关测试模型和策略的洞察力,以提高移动设备中的系统级ESD保护。

测试ESD模型和波形

这human body and its clothing can store between 500 V and 2,500 V of electrostatic charge during a day, but a human can only feel ESD pulses that are between 3,000 and 4,000 V. This is far above the level that damages electronic circuits, even if a human can’t detect it.

设计师必须在各个点 - 在组件制造商处,在设计阶段和设计工作结束时解决ESD。简而言之,ESD保护需要多方面的方法。

Typically, integrated circuit (IC) manufacturers design, test and qualify their ICs according to ESD industry standards. This protects against physical damage during IC production or assembly onto PC boards. The two tests that are typically used for ESD include the following:

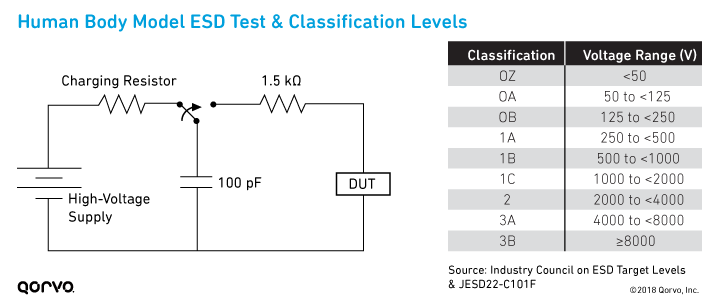

- 人体模型(HBM)。该测试模拟了一种ESD事件,其中人体通过触摸IC来排出累积的静电电荷。它由带电100PF电容和1.5kΩ放电电阻建模。

- 带电设备模型(CDM)。该测试模拟生产设备和过程中发生的充电和放电事件。该装置通过一些摩擦过程或静电感应过程获取充电,然后突然接触接地物体或表面。

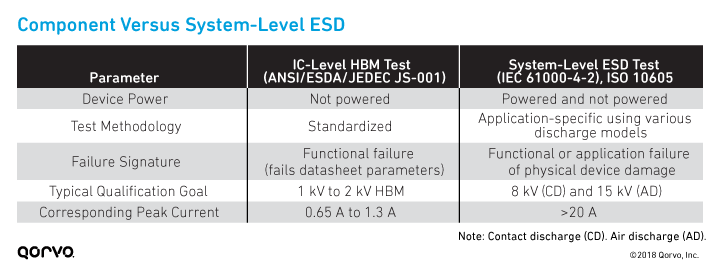

虽然设备级测试有助于提供IC的ESD稳健性的衡量标准,但系统级测试测量在现场(即,在原始设备制造商[OEM]设备或最终产品中)时的电子设备的保护。

To best understand the ESD protection required for a final product, the OEM should design使用系统级ESD方法and then test the final product according to theInternational Electrotechnical Commission (IEC)ESD标准61000-4-2。IEC 61000-4-2被认为是最终产品ESD测试和评级的行业标准。此测试确定系统对字段中的外部ESD事件的漏洞。

下图比较了三种脉冲中的能量和峰值电流的量:

- 系统级IEC 61000-4-2

- 设备级HBM

- 设备级CDM

IEC ESD事件脉冲明显更强,因此对系统中的设备更难以通过。虽然设备级测试(HBM和CDM)有用,但为ESD稳健性提供了基线,但它并不总是在系统级IEC测试期间确定生存能力。

To display this concept further, the following table shows the differences between component testing and system-level IEC testing. As you can see, there’s a big difference — the system stress levels are higher.这takeaway:系统设计必须满足比设备级设计更严格的要求。

测试不足的问题

在开发过程中执行系统级ESD测试可能是有问题的。例如,在评估/不完整板组件上测试ESD并不提供完整的图片。结果这些组件不保证完成系统中的最终结果。

设计设备级ESD测试(即,HBM和CDM)旨在为具有适当ESD控件的工厂中的离散组件产生可重复和可重复的结果。这被称为一个ESD protected area (EPA)。However, these tests aren’t intended to address the full range of real-world product-level ESD events outside of the EPA.

这key to product robustness: System-level ESD

Instead, the key to an ESD-robust system design is to consider the effects of ESD in the system. To obtain a system-level perspective, it’s paramount that designers understand and address the following:

- 系统级应力事件及其对整个产品的影响。设备级ESD测试结果为系统ESD设计提供最小信息,因为它们无法反映IEC ESD事件期间的电子设备体验。

- 这board-level interactions in the system,along with the transient behavior of the pins that contact the outside of the electronic part during ESD stress.

- 高效表征方法像组件级别transmission line pulse (TLP)数据, to analyze the IC, board and system interactions.

System-level ESD protection strategies depend on physical design, product requirements and product cost.

进入深度

了解有关Syste-Level ESD的更多信息:

最佳方法:系统高效的ESD设计(种子)

System-efficient ESD design (SEED)is a system-level approach that considers the transient responses of all components in the system. SEED methodology also includes the physical effect of an IEC stress applied at the external port of the PC board on the IC pin.

种子是一种协同设计方法,可实现板载和片上ESD保护。使用种子,您分析和实现系统级ESD稳健性。该方法需要全面了解ESD应力事件期间外部ESD脉冲,全系统级板设计和设备引脚特性之间的相互作用。

种子方法是系统和强大的系统级ESD保护的最佳方法。如下图所示,种子使用以下设计系统级ESD保护:

- Quasi-Static TLPcurrent-voltage (I-V) curve数据

- 瞬态模拟

- S-parameter PC board data

- IC I-V电路测量

We'll go into the details of SEED inPart 2andPart 3这个博客系列。但作为种子的一般介绍:

- 这PC board’sESD protection forms theprimary protection,防止IC或系统的物理损坏。

- 这on-chip保护服务A.secondary protection角色。

种子的基本概念是限制损坏的ESD脉冲到达内部IC引脚。通过执行和分析ESD系统级模拟来实现适当的系统级ESD设计。

接下来:RF前端设计的ESD保护策略

它没有秘密,在您的移动设计中战略性地接近ESD是很重要的。这样做减少了设计工程循环时间,ESD故障和研发费用。

在这个三部分博客系列中的下一篇文章中,我们进一步挖掘ESD保护组件和不同的策略减轻ESD对移动RF设计的影响。第3部分将解释如何使用种子方法,仿真和建模to determine your system-level ESD protection.

阅读我们系列中的所有博客关于克服移动设备中的ESD挑战:

- 第1部分:Get Grounded: What You Need to Know About ESD and RF Devices(this post)

- Part 2:移动设备的ESD设计策略:您的种子工具

- Part 3:优化ESD RF前端设计的种子方法

Have another topic that you would like Qorvo experts to cover?将您的建议发送给您的建议Qorvo博客团队它可以在即将到来的帖子中得到特色。请在电子邮件正文中包含您的联系信息。